1 Principios oscilador sinusoidal 2 Estructura oscilador sinusoidal 3 Osciladores RC - Amp. Op. 4 Osciladores Cristal 5 Consideraciones prácticas 6 Multivibrador astable 7 Generador onda triangular 8 Temporizadores integrados 9 Temporizadores XR-2240, MC1451D 10 Generadores monolíticos 566, ICL8038

10.9.- Temporizadores integrados

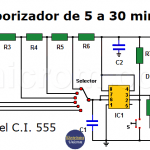

Existen en el mercado un conjunto de circuitos integrados denominados temporizadores (timers) especialmente diseñados para realizar multivibradores monoestables y astables.

El temporizador 555 (NE555 de Signetics en versión bipolar y TLC555 de Texas Instruments en versión CMOS) es un circuito integrado barato y muy popular que fue desarrollado en 1972 por Signetics Corporation.

En la figura 10.15 se muestra el diagrama circuital de este temporizador. Está constituido por dos comparadores, un flip-flop SR y un transistor que actúa como un elemento de conmutación. Las tres resistencias en serie de valor R definen las tensiones de comparación a 1/3Vcc y 2/3Vcc. En la figura 10.16 se presenta al 555 en la configuración monoestable.

Al aplicar un pulso negativo en Vi con una tensión inferior a 1/3Vcc, el condensador C se carga libremente a través de R. Este proceso de carga finalizará cuando la VC =2/3Vcc, en cuyo se produce la descarga brusca de C a través del transistor de salida.

El pulso de salida tiene una duración T, especificado por el tiempo que tarda el condensador en pasar de ~0V a 2/3Vcc, viene definido por la siguiente ecuación

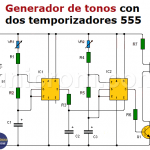

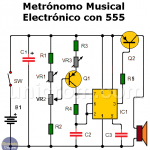

En la figura 10.17 se presenta al 555 en la configuración multivibrador astable. En este caso el condensador varía su tensión entre 1/3VCC y 2/3VCC. El proceso de carga se realiza a través de RA+RB y el de descarga a través de RB. Como resultado se genera a la salida una onda cuadrada no-simétrica definido por dos tiempos T1 y T2.

El porcentaje de ocupación del ciclo ( cicle) viene definido por:

Obsérvese que el duty cycle es mayor que 0.5 (50%) lo que significa que la onda cuadrada no es simétrica y la duración del estado lógico alto es mayor que el bajo (T1> T2).

Tut_temporizadores_integrados Tut_temporizadores_integrados_555_astable

1 Principios oscilador sinusoidal 2 Estructura oscilador sinusoidal 3 Osciladores RC - Amp. Op. 4 Osciladores Cristal 5 Consideraciones prácticas 6 Multivibrador astable 7 Generador onda triangular 8 Temporizadores integrados 9 Temporizadores XR-2240, MC1451D 10 Generadores monolíticos 566, ICL8038